NVIDIA belum lama ini merilis CPU “Vera” sebagai System-on-Chip (SoC) mandiri yang ditujukan untuk pihak ketiga, sekaligus memposisikannya sebagai pesaing langsung Intel Xeon dan AMD EPYC di segmen prosesor server. Namun, di balik ambisi tersebut, generasi Vera dilaporkan memiliki kelemahan kompatibilitas perangkat keras yang berdampak pada penggunaan GPU atau akselerator non-NVIDIA.

Berbeda dengan CPU server pada umumnya yang bersifat general-purpose dan dirancang agar dapat bekerja dengan akselerator dari berbagai vendor, Vera tampaknya dioptimalkan secara spesifik untuk ekosistem GPU NVIDIA. Ditemukan adanya bug perangkat keras pada pengendali PCIe yang dapat memicu kesalahan serius ketika dipasangkan dengan GPU AMD atau akselerator pihak ketiga lainnya, hingga menyebabkan kegagalan instalasi sistem dan operasi yang tidak stabil.

Akar masalah ini terletak pada cara pengendali PCIe di CPU Vera menghasilkan alamat memori. Dalam kondisi tertentu, CPU dapat menghasilkan alamat yang tidak valid saat melakukan operasi PCIe Memory-Mapped I/O (MMIO), khususnya ketika terjadi penulisan dengan partial byte enable ke area MMIO. Masalah tersebut menjadi lebih parah ketika area MMIO dipetakan menggunakan atribut memori Arm Normal Non-Cacheable (MT_NORMAL_NC).

Karena model memori Arm untuk atribut non-cacheable bersifat lebih longgar dalam pengurutan (memory ordering), kondisi ini dapat memicu erratum yang berujung pada kesalahan alamat, korupsi data, hingga kegagalan perangkat PCIe. Dampaknya paling terasa pada beban kerja intensif seperti pelatihan AI atau simulasi HPC berskala besar yang sangat bergantung pada operasi DMA.

Menariknya, masalah ini tidak muncul saat CPU Vera dipasangkan dengan GPU NVIDIA. Hal ini disebabkan karena GPU NVIDIA dirancang dengan mempertimbangkan karakteristik pengurutan memori spesifik dari Vera, sehingga kedua komponen tersebut dapat bekerja selaras tanpa memicu bug yang sama.

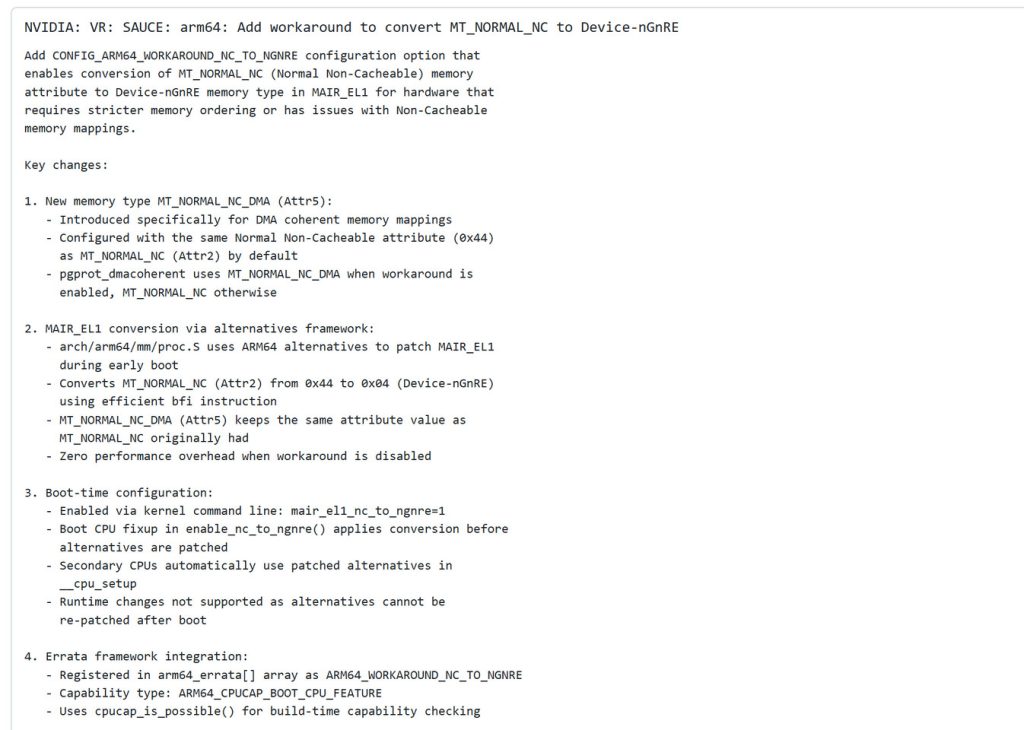

Untuk akselerator dari vendor lain, NVIDIA mengandalkan mitigasi melalui kernel Linux khusus. Dalam kernel internal NVIDIA, terdapat patch yang mengonversi pemetaan memori dari MT_NORMAL_NC menjadi Device-nGnRE (non-Gathering, non-Reordering, Early acknowledgement). Pendekatan ini memaksa pengurutan memori yang lebih ketat pada pemetaan DMA-coherent, sehingga mencegah terjadinya kesalahan alamat. Meski demikian, solusi ini berpotensi menimbulkan latensi yang lebih tinggi pada beberapa beban kerja I/O-sensitif dibandingkan mode non-cacheable normal.

Kasus ini bukan yang pertama di ekosistem Arm. Prosesor Arm-based dari Ampere Computing juga diketahui mengalami masalah serupa, di mana pengendali PCIe menghasilkan alamat tidak valid pada kondisi tertentu. Ampere menangani isu tersebut melalui modifikasi kernel Linux berbasis runtime, yang sejauh ini dilaporkan tidak menimbulkan degradasi performa signifikan. Hal ini mengindikasikan bahwa karakteristik penanganan memori Arm untuk perangkat eksternal kemungkinan menjadi faktor mendasar dari permasalahan tersebut.

Dengan temuan ini, CPU NVIDIA Vera dinilai masih memiliki keterbatasan serius dalam skenario heterogen yang melibatkan akselerator non-NVIDIA. Bagi data center dan penyedia infrastruktur yang mengandalkan kombinasi perangkat dari berbagai vendor, isu kompatibilitas ini menjadi faktor penting yang perlu dipertimbangkan sebelum mengadopsi platform Vera secara luas.