Marvell Ungkap Antarmuka Die-to-Die 64 Gbps Pertama di Dunia untuk Chiplet 2nm Generasi Selanjutnya

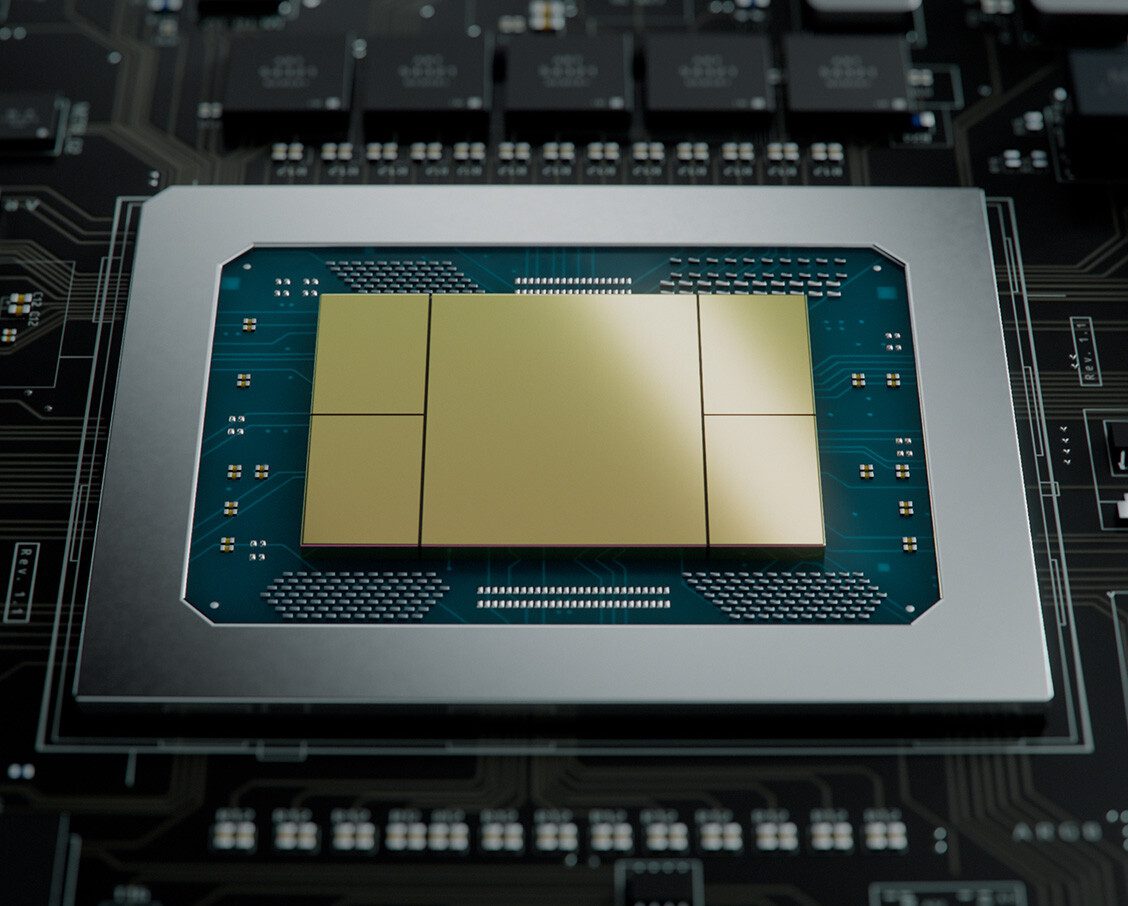

Marvell Technology resmi memperkenalkan Wire 64G XSR+, antarmuka die-to-die (D2D) pertama di industri yang mampu mencapai kecepatan 64 Gbps secara dua arah (bi-directional) dan dirancang khusus untuk proses manufaktur 2nm. Teknologi ini akan menjadi fondasi komunikasi antar chiplet dalam XPU generasi mendatang, termasuk CPU, GPU, AI accelerator, dan custom silicon lainnya.

Terobosan dalam Interkoneksi Chiplet

Wire 64G XSR+ dirancang untuk menjawab tantangan integrasi chiplet di era komputasi performa tinggi. Alih-alih menggunakan satu monolitik die, banyak produsen kini membagi komponen prosesor menjadi beberapa chiplet kecil yang dihubungkan melalui antarmuka internal berkecepatan tinggi. Fitur unggulan dari Wire 64G XSR+ meliputi:

- Bandwidth hingga 64 Gbps per jalur (lane) dalam konfigurasi full-duplex

- Jarak koneksi pendek ultra-rendah latensi, ideal untuk integrasi dalam satu paket (package)

- Konsumsi daya sangat rendah, menjadikannya ideal untuk arsitektur komputasi heterogen

Teknologi ini memenuhi spesifikasi UCIe (Universal Chiplet Interconnect Express) dan mendukung integrasi lintas vendor melalui IP reuse dan standardisasi protokol.

Siap untuk Proses 2nm dan Sistem AI/ML Masa Depan

Marvell mengklaim bahwa Wire 64G XSR+ telah disiapkan untuk proses fabrikasi 2nm, memposisikannya sebagai solusi siap produksi untuk era node sub-3nm. Antarmuka ini sangat relevan dalam pengembangan:

- XPU (multi-purpose processing unit) yang menggabungkan CPU, GPU, dan NPU dalam satu paket

- Sistem AI inference dan training berskala besar

- SoC kustom untuk data center dan aplikasi otomotif canggih

Dengan peningkatan efisiensi dan skalabilitas, arsitektur chiplet berbasis interkoneksi cepat ini menjadi kunci untuk memenuhi permintaan beban kerja AI generatif dan komputasi edge yang terus meningkat.

Mendukung Ekosistem IP dan Time-to-Market Lebih Cepat

Wire 64G XSR+ ditawarkan sebagai IP blok siap integrasi, memungkinkan perusahaan desain chip untuk mempercepat pengembangan produk tanpa harus membangun interkoneksi dari nol. Solusi ini kompatibel dengan portofolio SerDes dan chiplet PHY dari Marvell, serta didesain untuk menyatu dalam ekosistem desain berbasis EDA modern.

Marvell juga menekankan fokus mereka terhadap interoperabilitas dan kolaborasi industri, membuka jalan untuk pengembangan ekosistem chiplet yang lebih terbuka dan modular.

Sumber: TechPowerUp