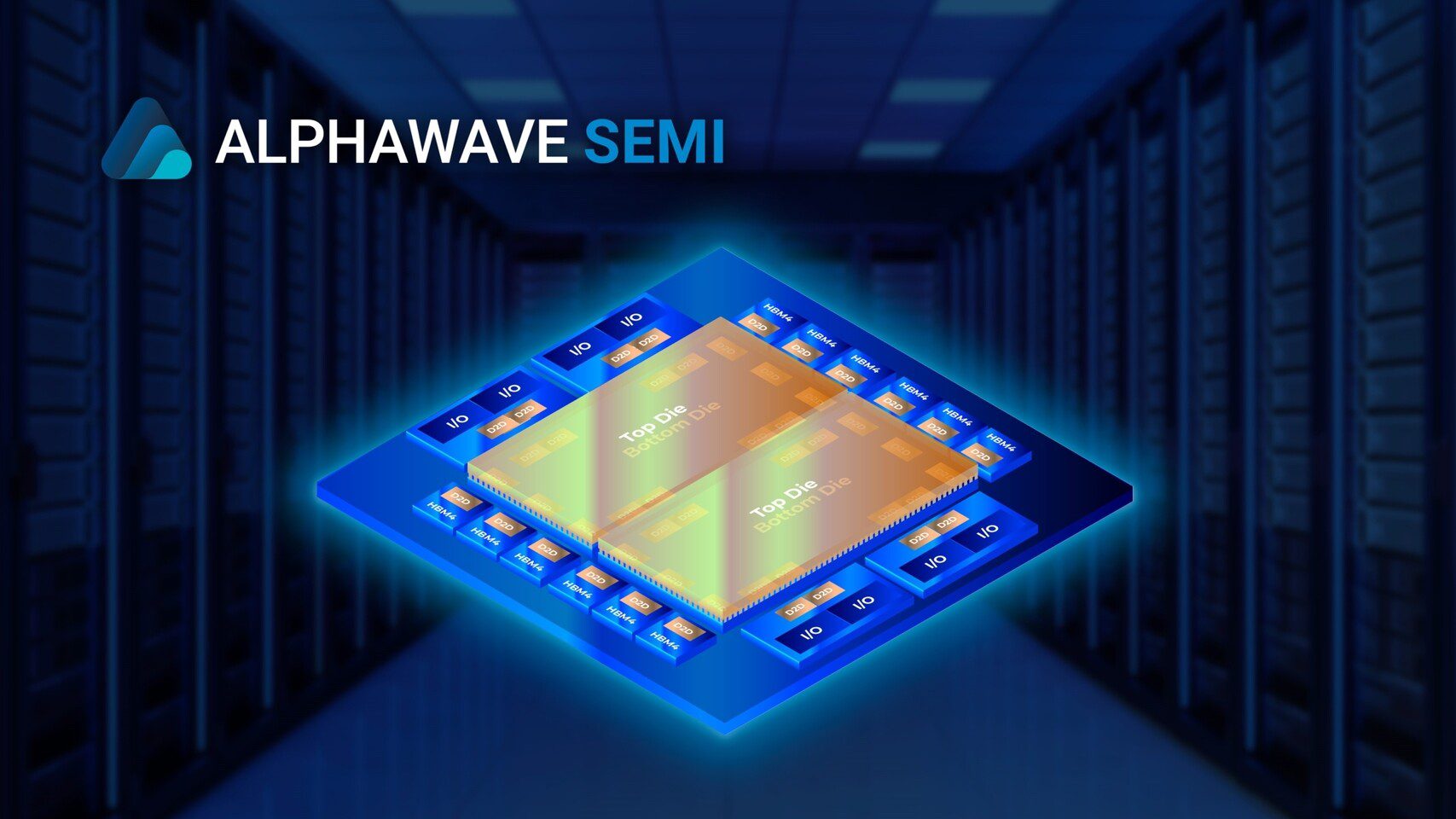

Alphawave Semi (LSE: AWE), pemimpin global dalam konektivitas berkecepatan tinggi dan silikon komputasi, resmi mengumumkan keberhasilan tape-out UCIe 3D IP pada teknologi TSMC SoIC-X, bagian dari platform 3DFabric. Pencapaian ini menandai evolusi penting dalam integrasi chiplet, sekaligus memperluas kapabilitas daya, efisiensi performa, dan bandwidth untuk aplikasi AI, pusat data, serta HPC generasi berikutnya.

Inovasi UCIe 3D untuk Era AI dan HPC

IP baru ini mendukung konfigurasi face-to-face (F2F) dengan peningkatan efisiensi daya hingga 10× dibanding antarmuka die-to-die 2.5D tradisional, serta kepadatan sinyal hingga 5× lebih tinggi.

Seiring meningkatnya kompleksitas model AI, keterbatasan desain planar konvensional—di mana komunikasi antar-chip hanya bisa terjadi di tepi silikon—tak lagi mencukupi. Industri kini bergerak menuju arsitektur disaggregated melalui advanced packaging: baik memperluas silikon secara horizontal di paket (2.5D) maupun menumpuk die secara vertikal (3D). Teknologi 3D die stacking diyakini sebagai jalur masa depan untuk efisiensi bandwidth dan daya yang lebih baik.

Detail Teknis

- Bottom die 5 nm mendukung TSV (Through-Silicon Via) untuk suplai daya dan ground.

- Top die 3 nm diposisikan di atasnya dengan integrasi vertikal penuh.

- 3DIO Portfolio: metodologi desain khusus Alphawave untuk mempercepat konstruksi dan verifikasi stack 3D.

Kolaborasi dengan Ekosistem Industri

- Siemens: Bermitra untuk menghadirkan solusi desain & verifikasi 3D IC, dengan fokus pada parameter listrik dan termal yang kritis.

- TSMC: Menyatakan bahwa kolaborasi ini memperlihatkan potensi nyata platform 3DFabric dalam menghadirkan efisiensi energi dan performa lebih tinggi untuk sistem AI generasi baru.

Tonggak Baru Setelah Tape-Out CoWoS 2 nm

Sebelumnya pada Juni, Alphawave Semi juga mengumumkan tape-out UCIe IP di proses 2 nm TSMC menggunakan teknologi 2.5D CoWoS. Kini, dengan hadirnya solusi UCIe 3D di SoIC-X, Alphawave menegaskan komitmennya untuk menghadirkan UCIe generasi berikutnya dengan dukungan 64G, menyasar pelanggan AI dan HPC yang terus beralih ke ekosistem chiplet.

Sumber: Alphawave Semi