Sarcina Technology, perusahaan pionir dalam desain paket semikonduktor dan fotonik, mengumumkan terobosan baru dalam metodologi interkoneksi chiplet berbasis UCIe-A (Universal Chiplet Interconnect Express-Advanced) dan UCIe-S (Standard). Inovasi ini mencakup desain interposer RDL (redistribution layer) yang dioptimalkan untuk koneksi die-to-die, mendukung kecepatan transfer hingga 32 GT/s dengan arsitektur perutean sinyal yang meminimalkan crosstalk sekaligus menjaga integritas sinyal.

Tantangan Chiplet untuk AI dan HPC

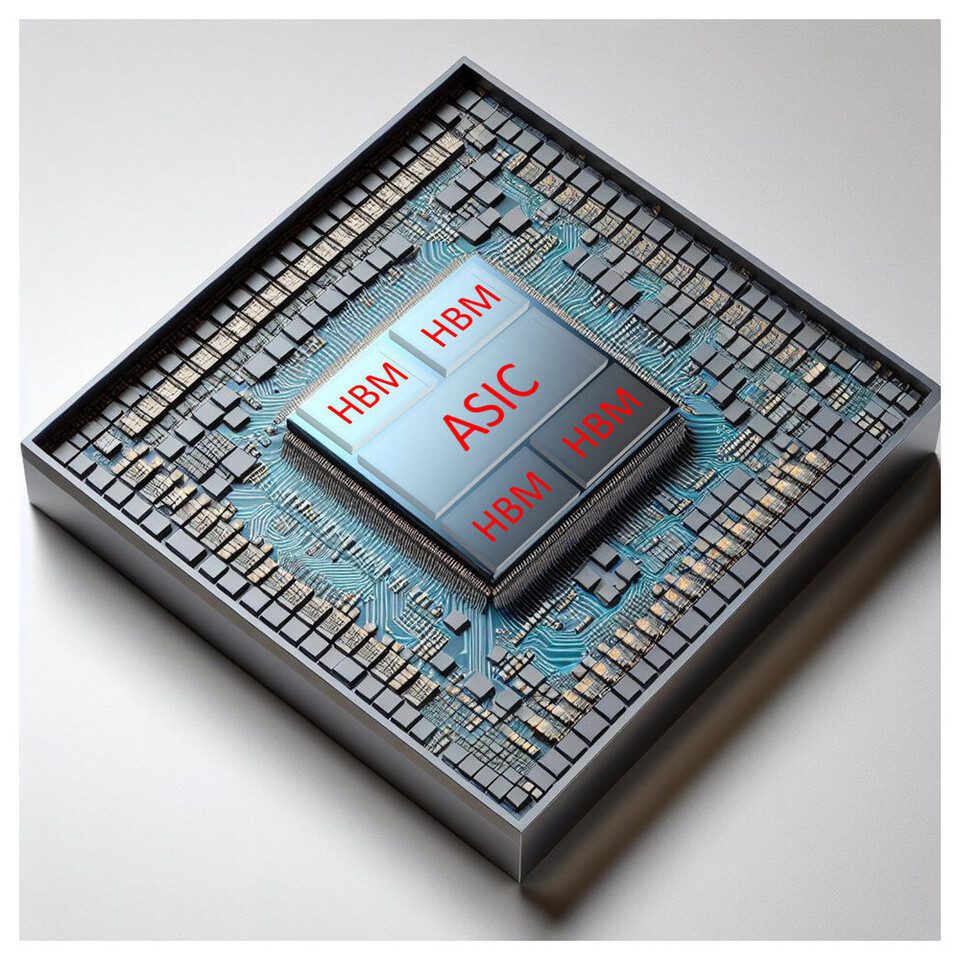

Dengan meningkatnya beban kerja AI yang sangat pesat, industri semikonduktor menghadapi keterbatasan sistem-on-chip (SoC) tradisional dalam ukuran, yield, dan biaya. Arsitektur berbasis chiplet dipandang sebagai solusi masa depan. Sarcina berfokus pada desain paket yang mampu mendukung performa sistem tingkat lanjut untuk akselerator AI dan komputasi berkinerja tinggi (HPC).

CEO Sarcina, Larry Zu, menjelaskan bahwa salah satu tantangan utama adalah mengatur interkoneksi agar meminimalkan crosstalk dalam ruang terbatas serta keterbatasan manufaktur, seperti jumlah lapisan tembaga yang dapat digunakan. Melalui simulasi elektromagnetik ekstensif, Sarcina memastikan solusi interposer barunya memenuhi standar ketat untuk insertion loss dan crosstalk, memungkinkan komunikasi bandwidth tinggi yang andal.

Inovasi UCIe-A

Metodologi baru UCIe-A berbasis interposer RDL menghadirkan:

- Transfer data die-to-die 32 GT/s, sesuai standar UCIe 2.0.

- Arsitektur routing yang mengurangi crosstalk secara signifikan.

- Pemanfaatan optimal ruang 3D dengan kanal routing terfokus di tepi die (beachfront).

- Routing multidimensi untuk data, clock, dan sinyal redundansi, mendukung desain kompak.

- Efisiensi biaya dengan lapisan RDL minimal tanpa melampaui batas manufaktur.

- Tata letak RDL standar untuk meningkatkan yield fabrikasi.

Inovasi UCIe-S

Untuk UCIe-S, Sarcina menargetkan substrat organik dan PCB berteknologi HDI dengan keunggulan:

- Insertion loss dan crosstalk minimal untuk jarak kanal panjang.

- Routing multilayer terstruktur di ruang 3D yang ringkas, memungkinkan tumpukan modul padat.

- Kompatibilitas dengan koneksi antar-paket di substrat organik atau PCB HDI.

- Performa 32 GT/s terverifikasi, mendukung adopsi UCIe 3.0.

- Komunikasi die-to-die yang tetap andal meski equalization pemancar dan penerima dinonaktifkan, mengurangi konsumsi daya.

Sinergi UCIe-A dan UCIe-S

Dengan menggabungkan UCIe-A dan UCIe-S, Sarcina menawarkan platform desain dan simulasi terpadu untuk interkoneksi chiplet lintas interposer, substrat, dan PCB. Hal ini memungkinkan pelanggan untuk:

- Memecah SoC monolitik menjadi chiplet demi yield dan efisiensi biaya lebih baik.

- Mengintegrasikan teknologi heterogen (komputasi, memori, analog, I/O) lintas node proses.

- Menggabungkan chiplet fotonik silikon dan unit array serat (FAU) dalam paket Co-Packaged Optics untuk menghilangkan bottleneck data.

- Menghadirkan solusi skalabel, efisien, dan berkinerja tinggi untuk akselerasi AI.

Larry Zu menegaskan:

“Kami tidak hanya merancang interkoneksi—kami membangun fondasi sistem AI generasi berikutnya. Keunggulan desain Sarcina terlihat jelas: performa lebih tinggi, area silikon minimal, biaya lebih rendah, efisiensi daya, dan kemudahan manufaktur.”

Sumber: Sarcina Technology