16 Agustus 2025 – TSMC dilaporkan tengah mempersiapkan langkah besar dalam teknologi kemasan chip dengan memperkenalkan CoPoS (Chip-on-Panel-on-Substrate), sebagai evolusi dari teknologi CoWoS (Chip-on-Wafer-on-Substrate) yang selama ini menjadi andalan untuk chip berperforma tinggi. Peralihan ini menandai upaya TSMC untuk memenuhi kebutuhan pasar yang semakin mendesak akan kapasitas integrasi lebih besar dan efisiensi manufaktur yang lebih baik.

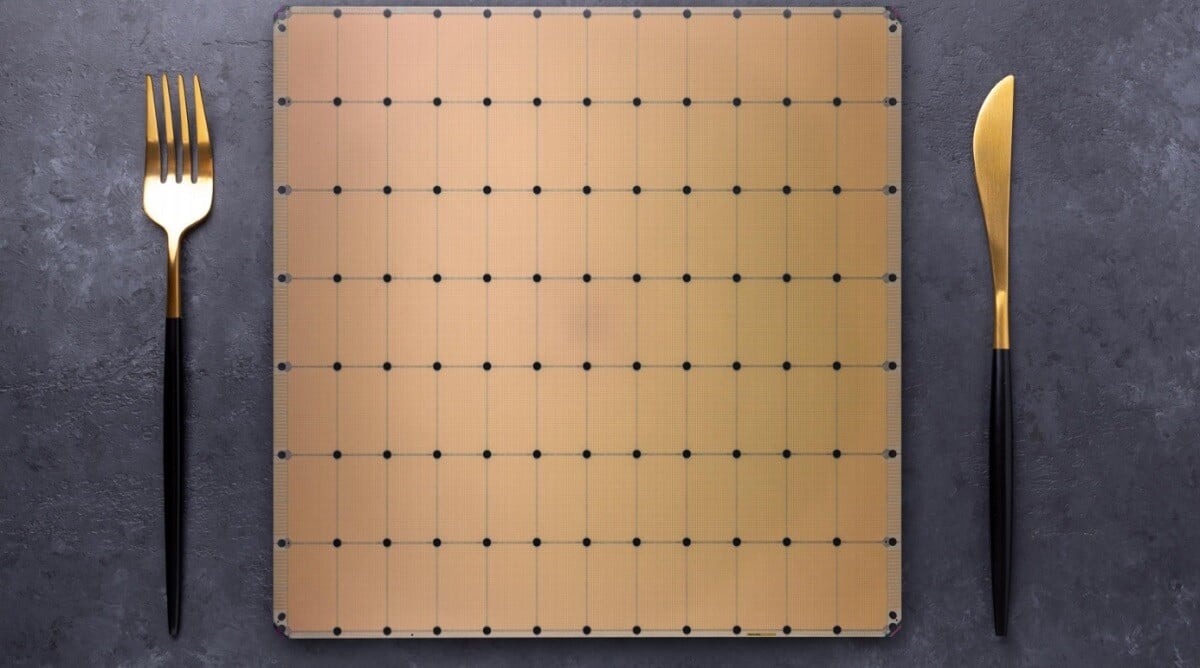

Dalam rencananya, TSMC akan menggunakan panel berukuran 750 × 620 mm, jauh lebih besar dibandingkan dengan wafer konvensional yang digunakan dalam CoWoS. Perubahan ukuran ini memungkinkan peningkatan signifikan pada jumlah chip yang dapat diproses sekaligus, sekaligus mengurangi biaya produksi per unit.

Teknologi CoPoS diharapkan memberikan keunggulan dalam mendukung chiplet architecture, tren yang semakin mendominasi desain prosesor modern, terutama untuk pusat data, AI, dan aplikasi komputasi berkinerja tinggi (HPC). Dengan panel yang lebih besar, integrasi multi-die dan interkoneksi bandwidth tinggi dapat dilakukan lebih efisien.

Langkah TSMC ini juga dilihat sebagai strategi untuk menjaga posisinya sebagai pemimpin global di bidang manufaktur semikonduktor, sekaligus menghadapi kompetisi dari pesaing utama seperti Samsung dan Intel. Adopsi panel skala besar berpotensi menjadi standar industri baru dalam dekade mendatang.

Bagi pelanggan, termasuk perusahaan pembuat prosesor dan akselerator AI, transisi ke CoPoS berarti akses pada solusi packaging yang lebih skalabel, hemat biaya, dan mampu menangani kompleksitas chip masa depan. Jika berhasil, teknologi ini akan menjadi fondasi penting bagi generasi prosesor berikutnya.

Sumber: TechPowerUp